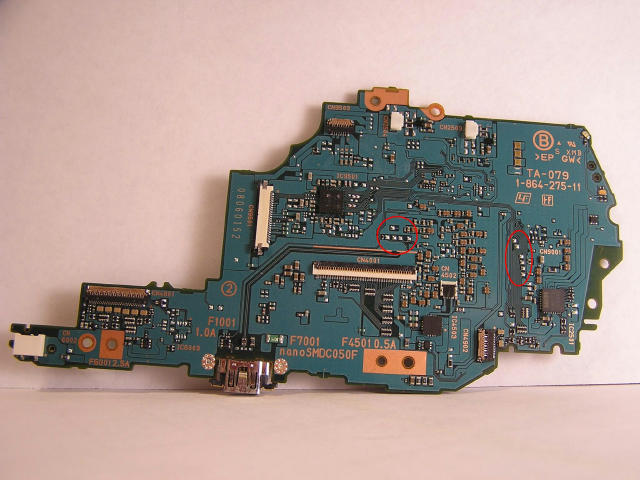

With the help of some university lecturer I have removed the flash chip from a psp board. Neither the board nor the chip are damaged. My idea is to build a PSP with 2 flash roms. If I brick one, I can restore it with other one. Everybody how has a bricked PSP can help Team Emergency Exit with giving us the board. I also need some money for build a circuit board to attach two on. Contact: mczonk@teamemergencyexit.com

The Good Facts

The chip is a standard chip from Samsung: K5E5658HCM . There is nothing secret with the chip. Everybody can buy it, if you take 1000 :D

The Bad Facts

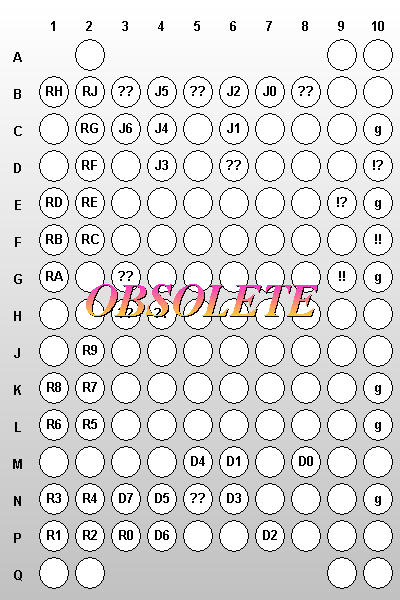

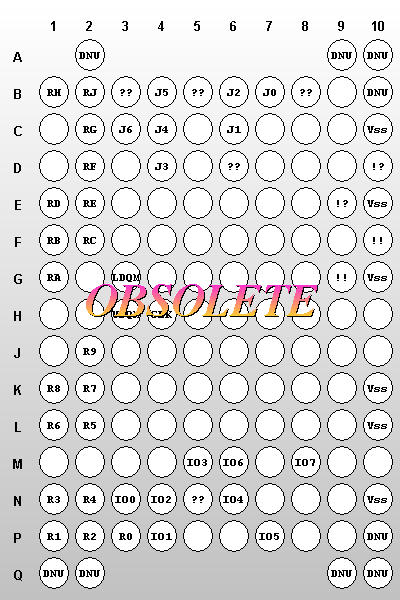

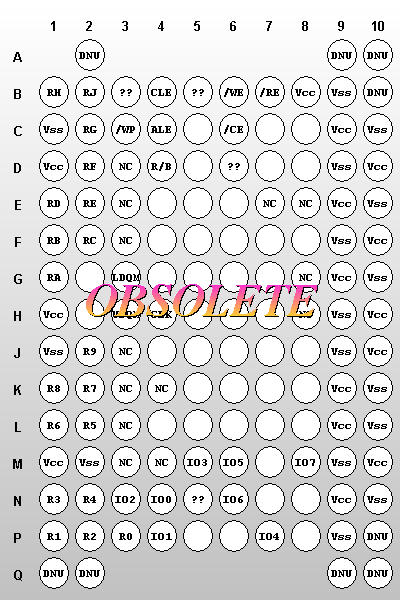

The chip is not only the flash rom (256 mbit nand rom). It is also the ram (256 mbit ddr ram). If you read though the datasheets of the chip, you will find there figures. The flash is built from nand gates. It won't be as easy as access nor gates. So direcly writing into the flash is not easy.

The Ugly Facts

If you look at the board, you will see the wire loops from processor to the flash/ram chip. These wires are made to keep all wires in the same length. This is important for the timing of the ram and timing is very very cirical. If I brought back the flash/ram on the board with just some small wire brigdes, it could disturb the timing of the ram. The flash is not critical, but the ram is.

I will also try to build a two flash psp.